|

|

The AmigaONE X1000 and X5000 from A-EON come equipped with a rather special, and as far as I know unique, feature for a personal computer -- a user programmable co-processor with its own expansion slot! |

Both the early model, the AmigaONE X1000, and its successor the X5000 come equipped with a powerful little companion processor, the XMOS XS1-L16A (formally the XS1-L2) 32-bit multi-core microcontroller, designated the "Xena" chip. The Xena chip is wired to both the main CPU and a custom 98 pin expansion slot called the "Xorro."

In this series of articles, I will be documenting my research into the Xena chip and its integration with the new Xorro expansion slot. Along the way, I hope to shed some light on the potential power of this unique creation opportunity that A-EON has brought to its latest line of AmigaONE computers, and to demonstrate how you can utilize it to create your own software and/or hardware projects.

In days past, the Commodore line of computers has enjoyed a wide range of custom hardware expansion options, many of which started out as simple hobby projects from a single individual or small group. Going back at least as far as the Commodore PET machines and carrying forward through the C64 and C128 line, Commodore included the "User Port" interface, which was essentially a combined parallel and serial port which connects to the MOS 6526 Complex Interface Adapter (CIA) chip. While Commodore may have intended this interface primarily for printers and modems, the ease of direct access to the CIA chip via PEEK and POKE commands in BASIC, and the fact that this interface was publicly documented, meant that before long Commodore users had their machines controlling everything from a lap counter for a R/C car track or automatically scoring a game of bowling, to balancing driveshafts at a garage in Poland!

Later on, as the Commodore Amiga started to appear on the scene, the user base got even more creative in finding ways to expand their favorite machines. Today, the home-brew project space has simply exploded with a whole new line of more accessible microcontrollers and Field Programmable Gate Arrays (FPGA) being employed in new hobby and professional projects every day.

By including the Xena chip and Xorro slot as an integrated part of the new AmigaONE machines, A-EON has taken custom home-brew (and professional) projects to a whole new level. Now, instead of designing your latest cool piece of hardware to interface with a fixed component like the CIA chip, you could tailor the on-board controller chip to work with your hardware. Imagine if you could completely redesign the internal logic of the CIA chip to work however you needed it to at the moment. Now imagine that instead of a single "logical thread" of operation, you could have 16 "logical threads" all running at the same time. Now imagine each of these threads could execute complex logic at a

guaranteed rate of 63 Million Instructions per Second (MIPS) simultaneously, and react to internal and external control lines within 10 nanoseconds (that's 10 billionth's of a second for those keeping track at home). Now imagine... OK, ok, I am getting ahead of myself. Let's start by taking a closer look at exactly which XMOS chip the Xena actually is.

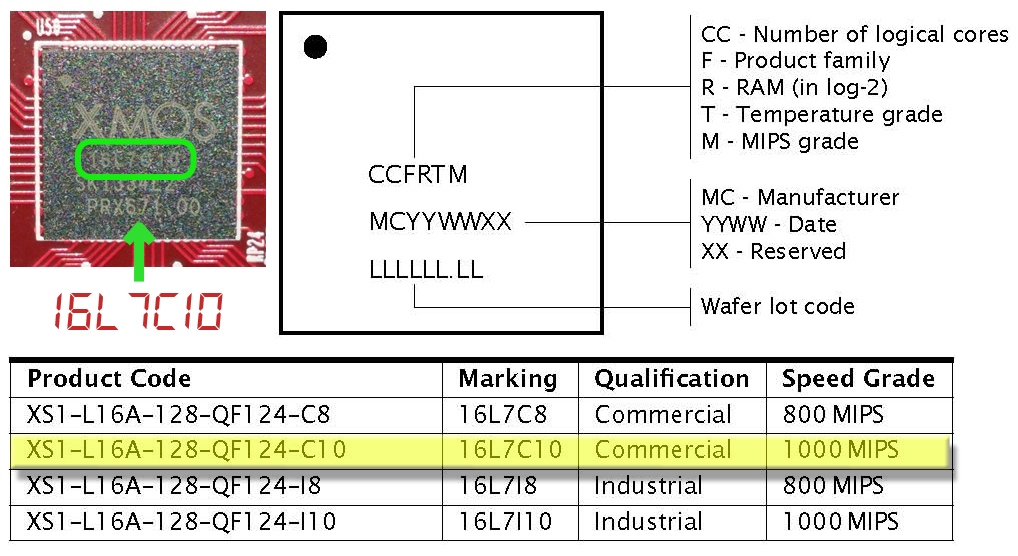

Taking a quick photo of the Xena chip on the AmigaONE X5000 and comparing the numbers on the chip with the "Part Marking" legend from XMOS, we deduce the following: the Xena chip is an 16L7C10. '16' for 16 Logical Cores, 'L' for the XMOS "General Purpose" product family, '7' indicates the RAM (in this case 128KB Total, 64KB in each Tile), 'C' for Commercial (Temperature grade), and '10' which notes the MIPS rating (in this case 1000 MIPS). According to the "Ordering Information" guide from XMOS, our chip's product code is "XS1-L16A-128-QF124-C10." Using this product number we can find out a great deal more about this chip. A quick Google search on this product number returns several items, most notably the direct download link for the XS1-L16A-128-QF124 Datasheet on the www.xmos.com website.

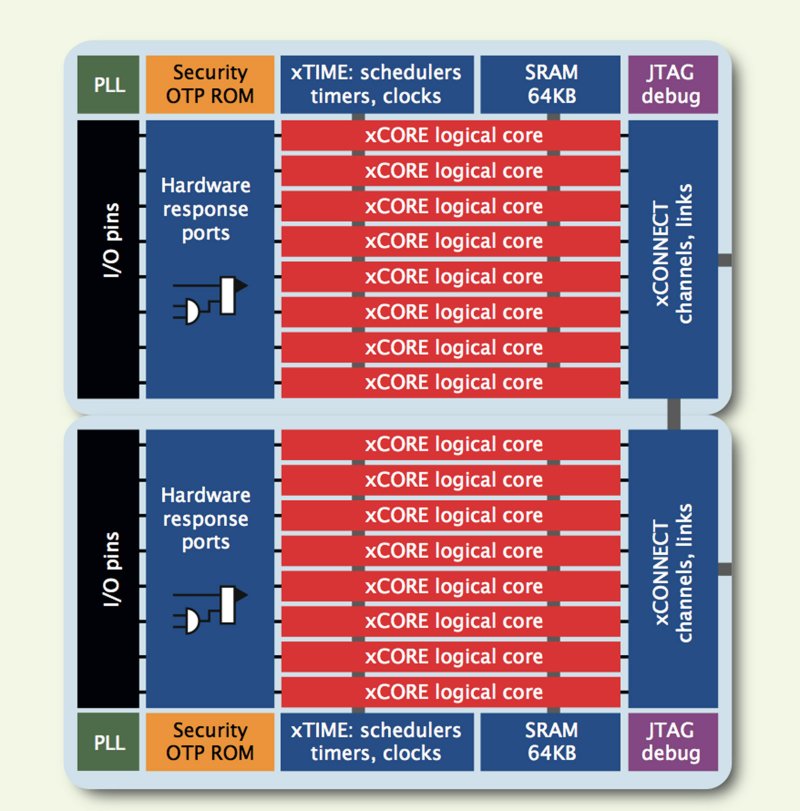

Now let's take closer look at a block diagram of the Xena (XMOS XS1-L16A) chip:

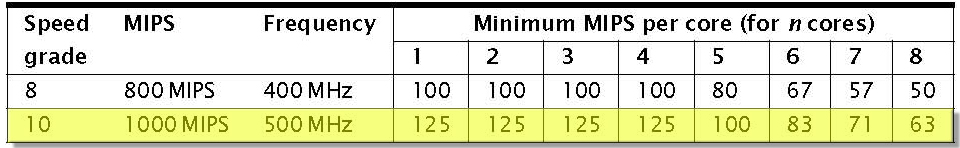

The Xena chip contains two processor cores, called "xCORE Tiles" and 16 "xCORE logical cores" (eight per Tile). It is clocked from a 25Mhz oscillator with its Phase-Locked Loop (PLL) configured for x20 operation, thus clocking the Xena chip at 500Mhz. The following chart details how the total rate of 1000 MIPS per Tile is distributed between the Logical Cores on that Tile. According to the XS1-L16A-128-QF124 Datasheet, if up to four logical cores are active then the available processing cycles are divided between the four cores, or in this case the first four cores each get 125 MIPS. Now, if more than four cores are active on the Tile, then the cycles are *at least* 1/n cycles for n cores, or in this case 5 cores get 100 MIPS each, 6 get 83 MIPS each, 7 gets 71 MIPS each, and if all eight cores are executing simultaneously on a given Tile, then they each get 63 MIPS.

Additionally, logical cores that are waiting on some event trigger or simply not assigned for use, are "asleep" and free up any processing cycles for other cores to use. This means that often the predicated rates per core may be higher, however these values are the guaranteed

minimum number of MIPS per core.

This is a very important distinction. During the normal execution of program threads running in a multitasking environment (like AmigaOS4 in this case), it is nearly impossible to determine the number of CPU processing cycles that a given thread will actually get. This is a factor of CPU load, task priority scheduling, etc. However, on the Xena chip your code is running on a dedicated 32-Bit Reduced Instruction Set Computing (RISC) architecture where every processor instruction (except divide) can be executed at a rate of one instruction per clock cycle. Equally, access to the internal SRAM (64KB per Tile) also runs at one fetch per cycle.

The XMOS multi-core programmable microcontollers fit a nice niche between single-threaded static microcontrollors and full FPGA chips. With built in Real-Time Operating System (RTOS) functionality in hardware, a 10 nanosecond response time to its Input/Output (I/O) lines, fully predictable execution times, and the ability to be programmed with an extended form of C called Cross-C (xC), the XMOS allows you to perform tasks in software which would normally require dedicated hardware to achieve.

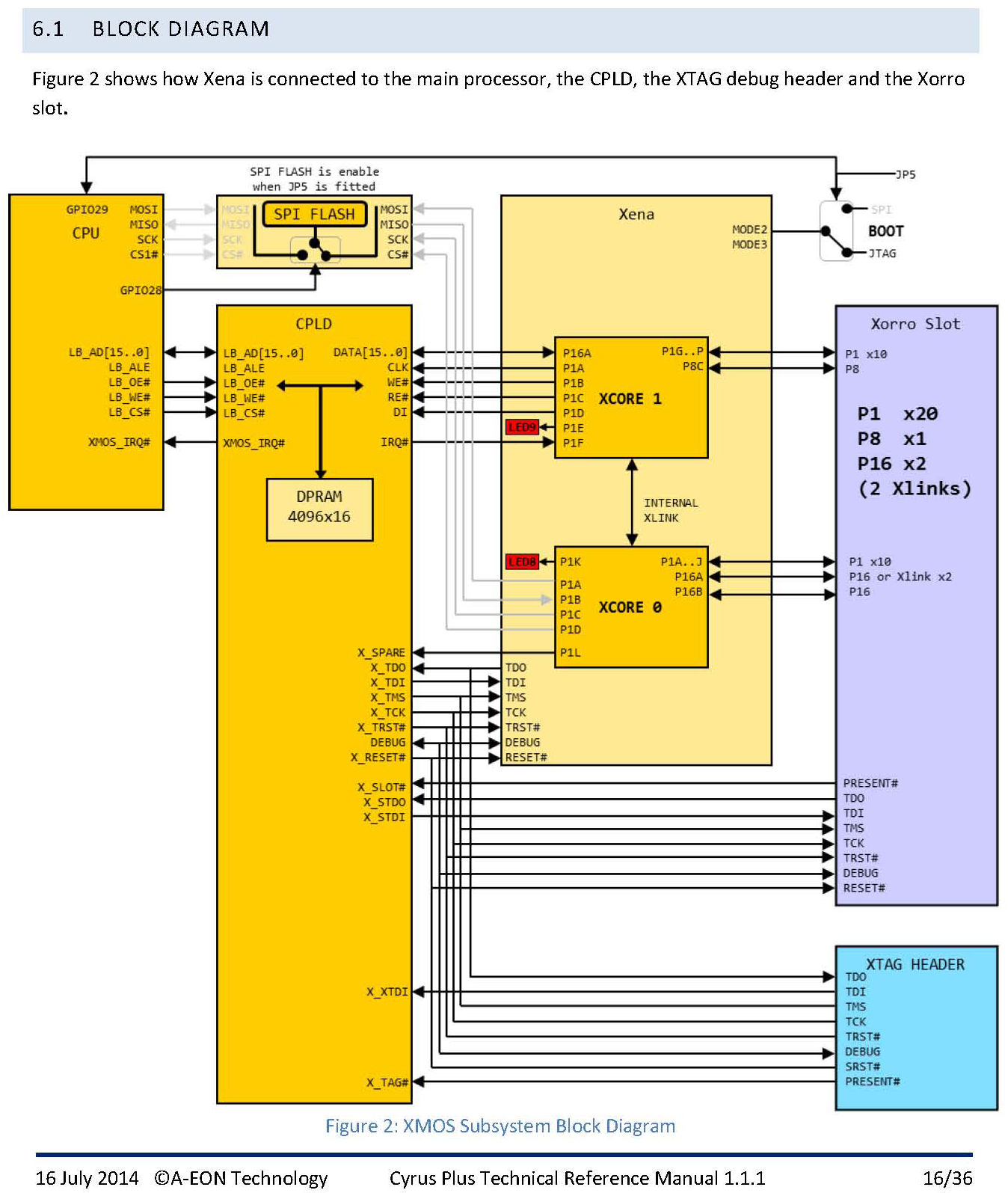

The Xena is wired on the motherboard of the AmigaONE X5000 so that it can communicate with the main CPU as well as to it's own dedicated expansion slot, called the "Xorro" slot. The "Xena" name is a nod to the Custom Chip sets of the Classic Commodore Amiga computers of the 80s and 90s, where the individual chips were referred to as "Agnus", "Alice", "Denise", "Paula", etc. The name "Xorro" is also a nod to the classic machines which had the "Zorro II/III" expansion subsystem. The modern Xorro slot is physically a PCI Express x8 (98 pin) card edge connector that is positioned in-line with a normal PCIe x1 expansion slot (both slots may be used simultaneously). While the Xorro slot may have the same physical connector as a standard PCIe x8 slot, it is not wired the same, nor is it compatible with standard PCI Express x8 cards.

Instead, the Xorro is connected directly to the on-board Xena chip via a series of Input/Output Ports as well as to the Xena's XLinks ports which allow it to connect to a daisy-chain of additional XMOS chips. This block diagram from the AmigaONE X5000 Technical Reference Manual (TRM) (reproduced here by permission from A-EON) gives us an idea of how the Xena chip connects to both the Xorro slot and the main CPU.

The XMOS-XS1 Architecture, which is Xena chip is, can be considered the modern successor to the famous Inmos Transputer technology of the 1980s which pioneered microchip architecture specifically intended for parallel computing.

More to the point, David May, a Professor of Computer Science at the University of Bristol was the architect of both the Transputer designs and the XMOS core technologies, and has 33 granted patents (with many pending patents) that center around microprocessor technology. He is also one of the original founders of XMOS when it was spun out from Bristol University. The XMOS-XS1 chips leverage a similar hardware-extendable parallel execution model as the Transputer chips did back in the day. Each XMOS-XS1 chip can contain one or more Tiles, and each Tile can have one or more Logical Cores. All Logical Cores can communicate with each other on the same Tile, and with other Logical Cores on other Tiles. Further, through Links to other XMOS-XS1 chips, they can seamlessly communicate with other Logical Cores on Tiles located within other XMOS-XS1 chips!

In the case of the AmigaONE X5000, this means that the Xena chip can have functions running in parallel on any of its 16 Local Cores (you could think of them like Hardware Threads). Each of these functions (or tasks) can interact with each other through a set of two Channel ends. Then, via the Xorro slot, you could add additional XMOS chips and directly extend the available processing capability.

The presence of the Xena chip and Xorro expansion slot on the AmigaONE X5000 opens the door to many possible commercial and user-created expansion options. The Xena may simply be used as a co-processor to the main CPU, or via the Xorro slot as a high performance controller of external hardware. The possibilities are limited only by the imagination of the user. It should be noted that in every other case (that I am aware of) the XMOS chips are programmed externally via a JTAG port, where as with the X5000 the JTAG interface is already connected to the CPU, allowing the Xena chip (and any further XMOS chips connected via the Xorro slot) to be programmed *from* the native AmigaOS4 Operating System. Additionally, the Xena chip could be programmed to interact with a native AmigaOS4 (PowerPC) application, extending it with real-time hardware performance levels of paralleling computing power. The X5000 motherboard still fully supports programming and debugging interfaces to external systems as well as its internal communication to the Xena, so you can take full advantage of XMOS development and debugging tools running on external hardware.

Hopefully, this introduction has given you some idea about what the Xena chip is, and got you thinking about what kind of applications may be created for it. In the next article I will go into more detail about what development tools exist, and how to get AmigaOS4 to load programs onto the Xena chip. In the mean time, here are a few links for additional reading that you may find interesting.

Reference:

XMOS XS1-L16A-128-QF124 Datasheet

Reference:

The XMOS XS1 Architecture

Reference:

Benchmarking I/O response speed of microprocessors - Research study University of Denver

This article has been translated into French by David Brunet and published on the Obligement website.

Read the French version of The Xena Research Project Blog here:

The Xena Research Project [French]

(If you wish to republish this Blog series, translated into another language, please contact me directly at

jamie@bitbybitsoftwaregroup.com for permission. I will then include links to official translations here and on my main website. Thanks.)

|

Jamie Krueger

Owner/Head Developer BITbyBIT Software Group LLC www.bitbybitsoftwaregroup.com |